- 您现在的位置:买卖IC网 > Sheet目录287 > 25LC640-E/P (Microchip Technology)IC EEPROM 64KBIT 2MHZ 8DIP

25AA640/25LC640

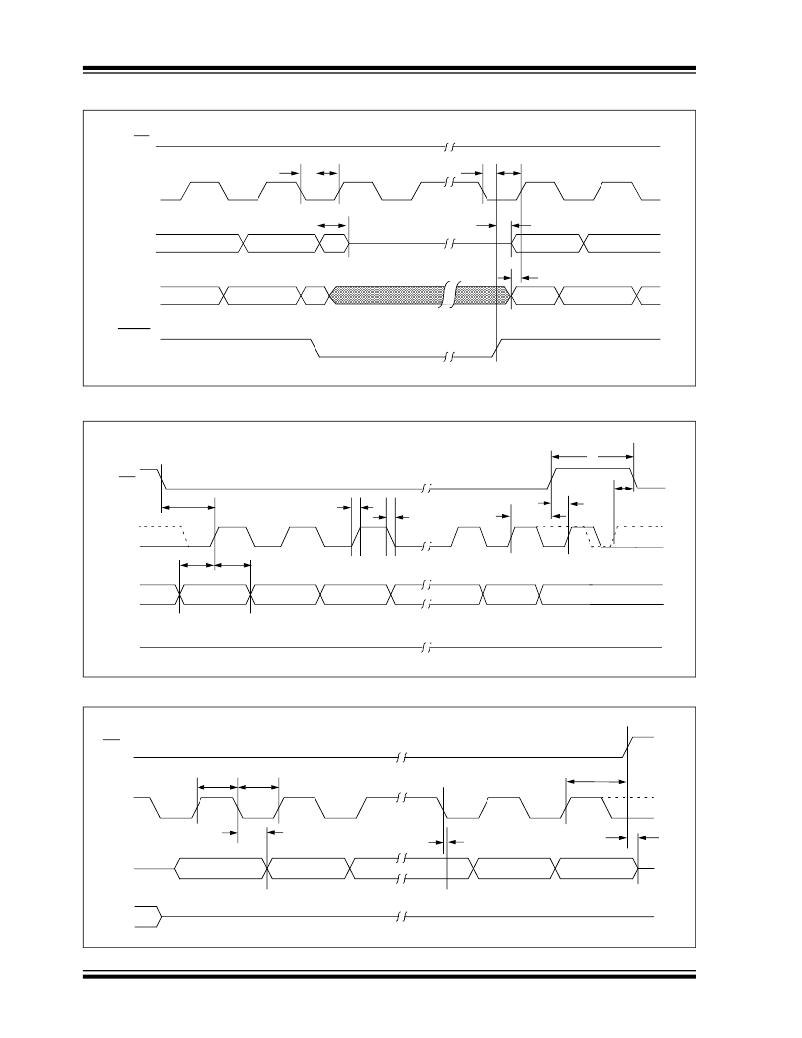

FIGURE 1-1:

CS

HOLD TIMING

1 6

17

16

17

SCK

18

19

SO

n+2

n+1

n

High-Impedance

n

n-1

Don’t Care

5

SI

n+2

n+1

n

n

n-1

HOLD

FIGURE 1-2:

SERIAL INPUT TIMING

4

CS

2

Mode 1 , 1

7

8

3

11

12

SCK Mode 0 , 0

5

6

SI

SO

FIGURE 1-3:

CS

MSB In

High-Impedance

SERIAL OUTPUT TIMING

LSB In

SCK

9

10

3

Mode 1 , 1

Mode 0 , 0

13

14

15

SO

SI

DS21223H-page 4

MSB Out

Don’t Care

LSB Out

? 2008 Microchip Technology Inc.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

25LC640A-E/P

IC EEPROM 64KBIT 10MHZ 8DIP

281708-4

PLUG HE14 IDC 90 4 P TUBE

281709-4

PLUG HE13 IDC 90 4 P AWG 24

281711-2

PLUG HE14 IDC 90 2 P TUBE

281783-8

PLUG HE14 IDC 180 8 P AWG 26-24

281784-5

PLUG HE13 IDC 180 5 P AWG 26-24

281786-8

PLUG HE14 IDC 180 8 P AWG 28-26

281789-8

PLUG HE14 IDC 180 2X8 P AWG26-24

相关代理商/技术参数

25LC640-E/PG

功能描述:电可擦除可编程只读存储器 8kx8 - 2.5V Lead Free Package

RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

25LC640E/SN

制造商:Microchip Technology Inc 功能描述:

25LC640-E/SN

功能描述:电可擦除可编程只读存储器 8kx8 - 2.5V RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

25LC640-E/SNG

功能描述:电可擦除可编程只读存储器 8kx8 - 2.5V Lead Free Package RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

25LC640-E/ST

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:64K SPI Bus Serial EEPROM

25LC640I/P

制造商:未知厂家 制造商全称:未知厂家 功能描述:Serial EEPROM 64K SPI Bus Serial EEPROM(129.03 k)

25LC640-I/P

功能描述:电可擦除可编程只读存储器 8kx8 - 2.5V RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

25LC640-I/P

制造商:Microchip Technology Inc 功能描述:EEPROM SERIAL 64K 25LC640 DIP8